博客

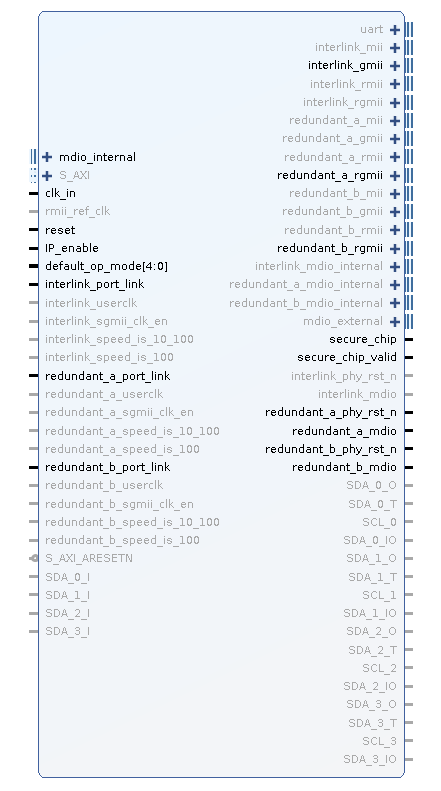

接口

- 全双工10/100/1000 Mbps以太网接口

- MII/RMII/GMII/RGMII/SGMII/QSGMII物理层设备(PHY)接口

- 每个端口支持不同的数据速率

- 铜缆和光纤介质接口:10/100/1000Base-T,100Base-FX,1000Base-X

交换

- 它通过硬件交换帧。此功能提供了很高的交换速度,是实现变电站自动化的过程总线和机架间总线的最大允许使用年限和数据完整性所必需的

- 处理体系结构专用于HSR/PRP。千兆以太网的转发延迟为500ns

- 它是一种全硬件。无需片上微处理器或软件堆栈

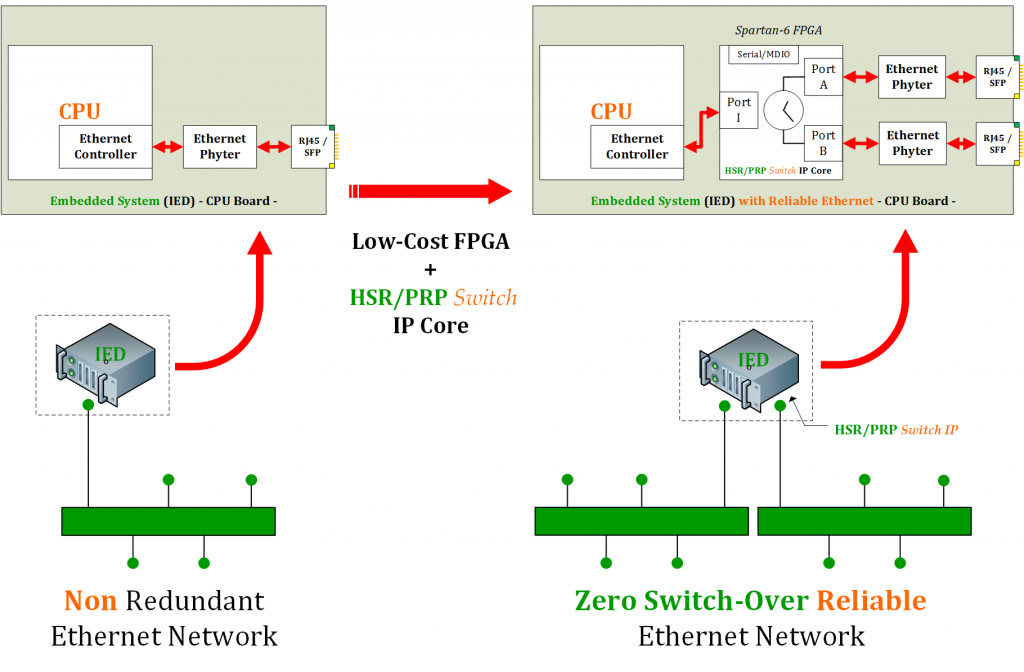

- 它已经过优化,几乎不需要逻辑资源,从而可以在低成本FPGA器件上实现

- 巨型帧管理

时间同步

- 它支持与SoC-e 1588 IP内核结合的IEEE 1588-2008 v2

冗余

- 它可用于实现终端节点DAN、RedBox或QuadBox功能

- 它带有单个标志,可以通过软件在PRP和HSR模式之间切换

- 它包括集成的每个端口的完整统计信息和错误寄存器(网络监督)

- HSR-HSR,HSR-PRP支持的模式用于无缝PRP-HSR网络合并和Quadbox操作

- VLAN支持和HSR环ID

- SNMP和MIB表可用

组态

- MDIO、UART、AXI4-Lite或CoE(以太网配置)管理接口

- 以太网配置(COE):通过连接到CPU的同一以太网链路全面访问内部寄存器

- 购买IP核时提供驱动程序

可定制功能,以优化资源/功能权衡

- 节点表大小

- 每个端口的转发队列大小独立

- 冗余和互连端口中的IEEE1588v2 P2P透明时钟

- 可扩展的复制/循环丢弃表

- VLAN优先级支持

- 通过AXI4-Lite、MDIO、UART或CoE(以太网配置)访问内部寄存器

- 具有集成SAN代理的RedBox模式

- IEEE 1588v2普通时钟、混合时钟和边界时钟

参考设计支持的板:

想了解更多信息,欢迎通过info@intelnect.com联系虹科

– 非冗余网络的 3 个端口参考与零丢包可靠网络的 3 个端口参考-

SOC-E SocTek系列可用于Xilinx Vivado工具的HSR/PRP交换机IP内核

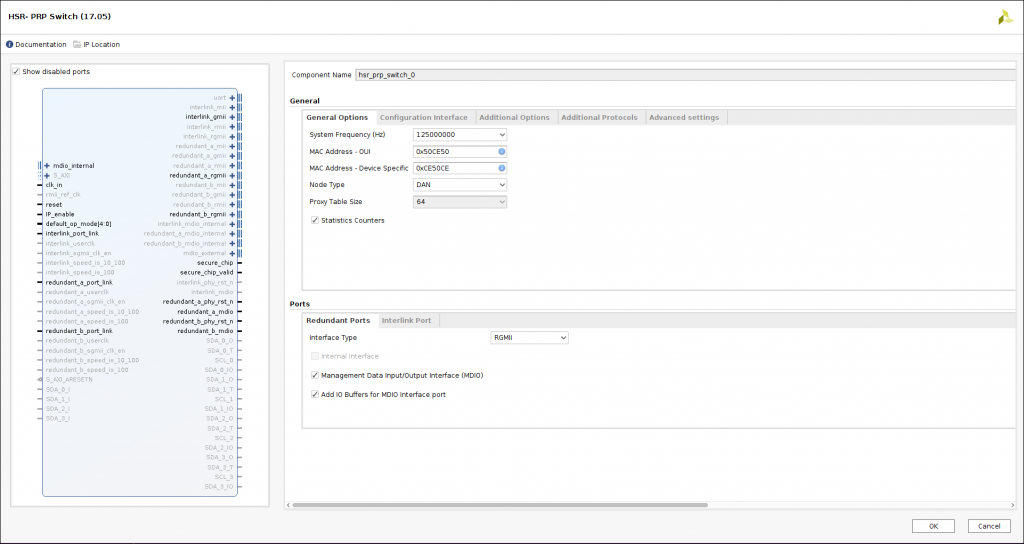

通过利用新的Xilinx Vivado工具,SOC-E SocTek系列HPS 可以轻松集成到你的FPGA设计中,该工具允许在图形用户界面中使用该IP内核,并以简便的方式配置IP参数。

以下Xilinx FPGA系列支持SOC-E SocTek系列HPS:

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

SOC-E SocTek系列产品推荐

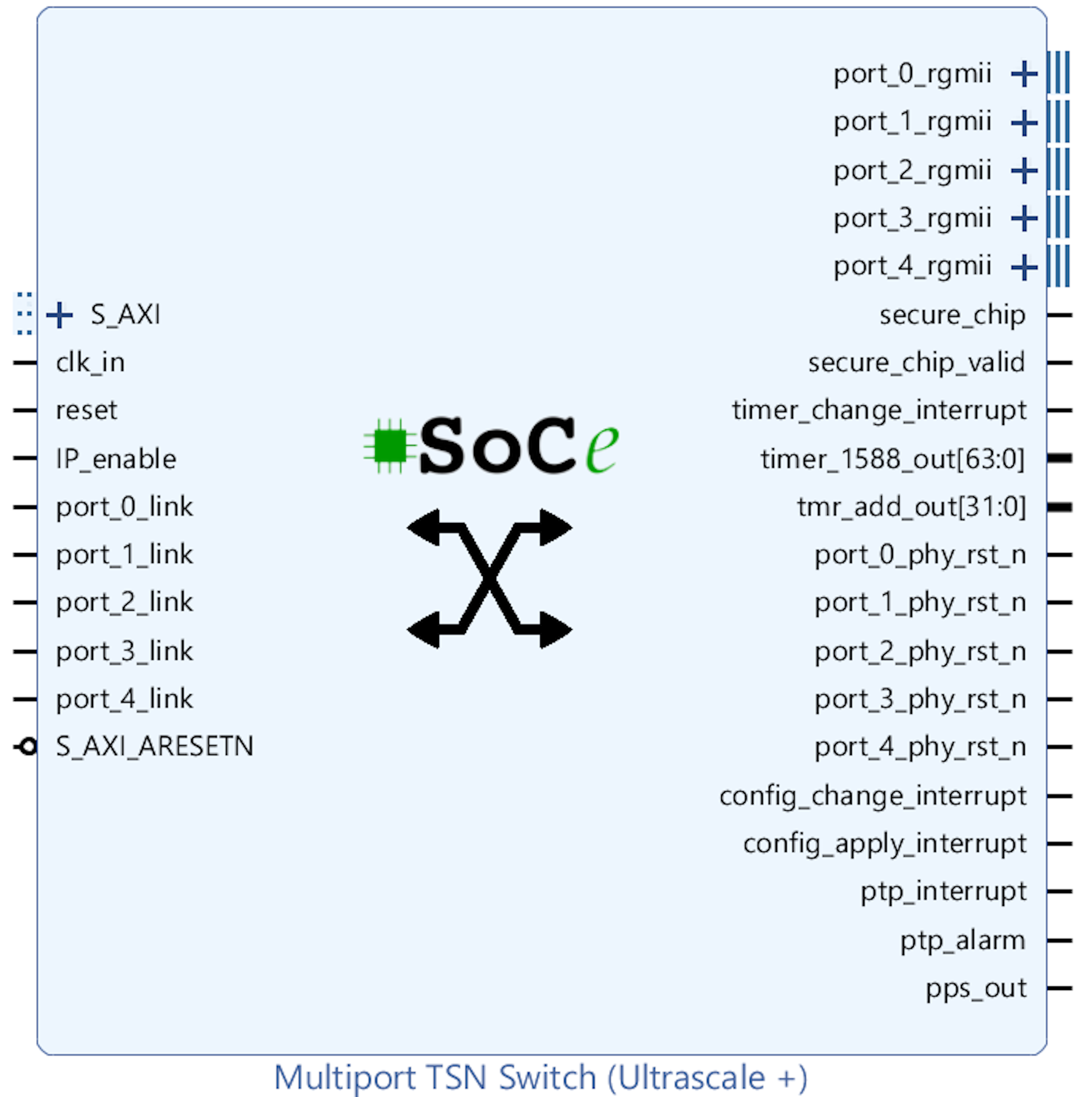

MTSN IPcore

全面的TSN解决方案,能够实现多种TSN协议规范

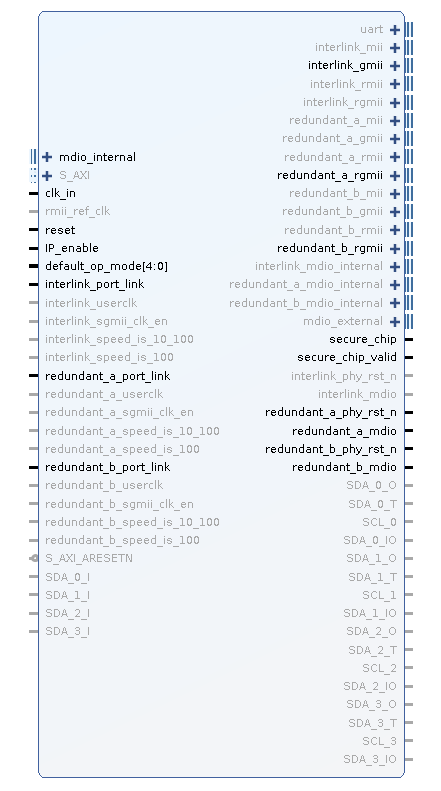

HSR/PRP/PTP IPcore

实现可靠性以太网通信的高可用性无缝冗余和并行冗余协议标准

网管/非网管IPcore

以太网交换机 IP 内核,面向可编程硬件平台

更多IPcore方案

减少设计和调试时间,加速开发进程