博客

主要特点

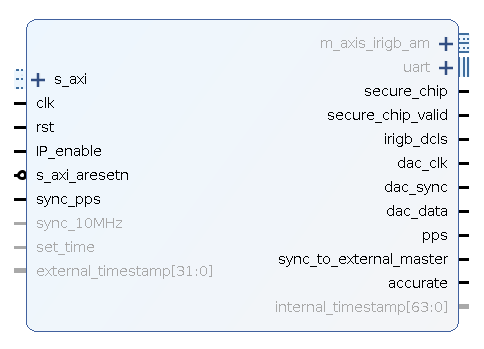

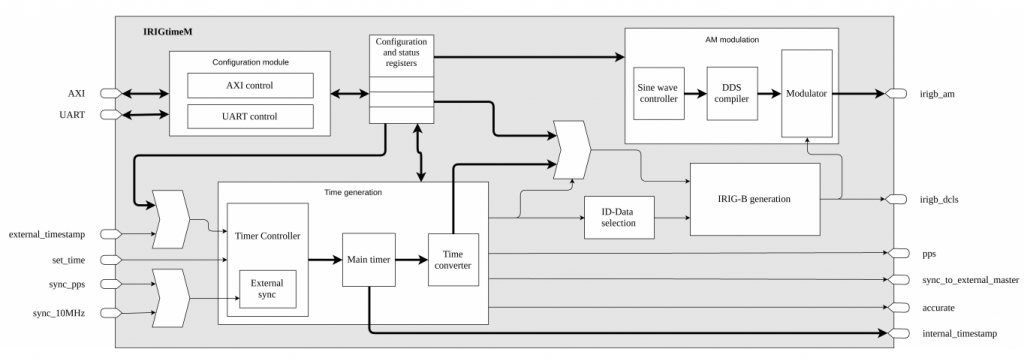

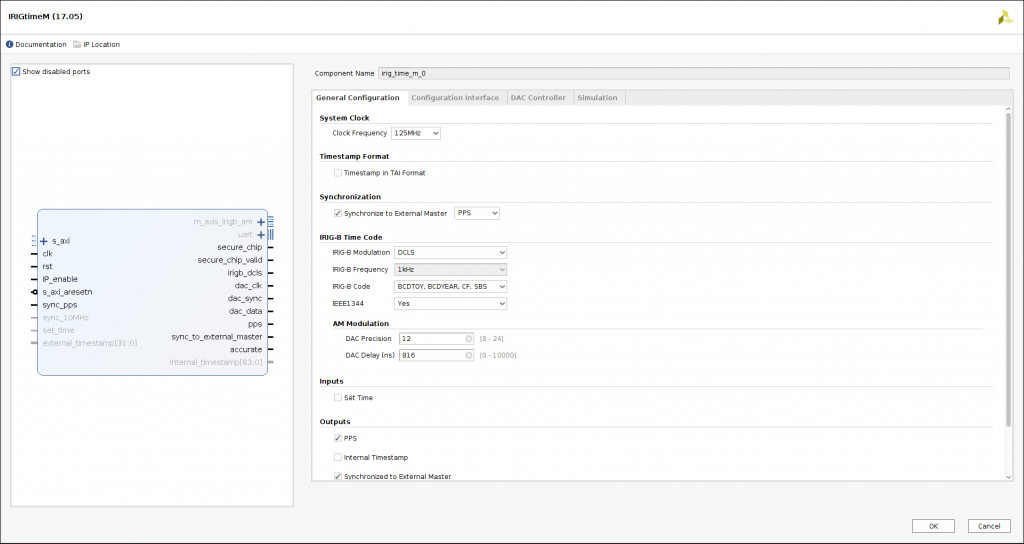

- 符合 IRIG 200-04 标准的时间同步主站

- 支持 DCLS 和 AM 调制

- 支持所有 IRIG-B 编码表达式,包括年份信息、控制函数和直二进制秒

- 输出类型(IRIG-B 时间码)可在实现之前和动态中配置

- 精确的 IRIG-B 输出,以提供纳秒级精度

- 用于 IP 初始设置的 32 位时间戳输入

- 用于测试的周期性脉冲输出

想了解更多信息,欢迎通过info@intelnect.com联系虹科

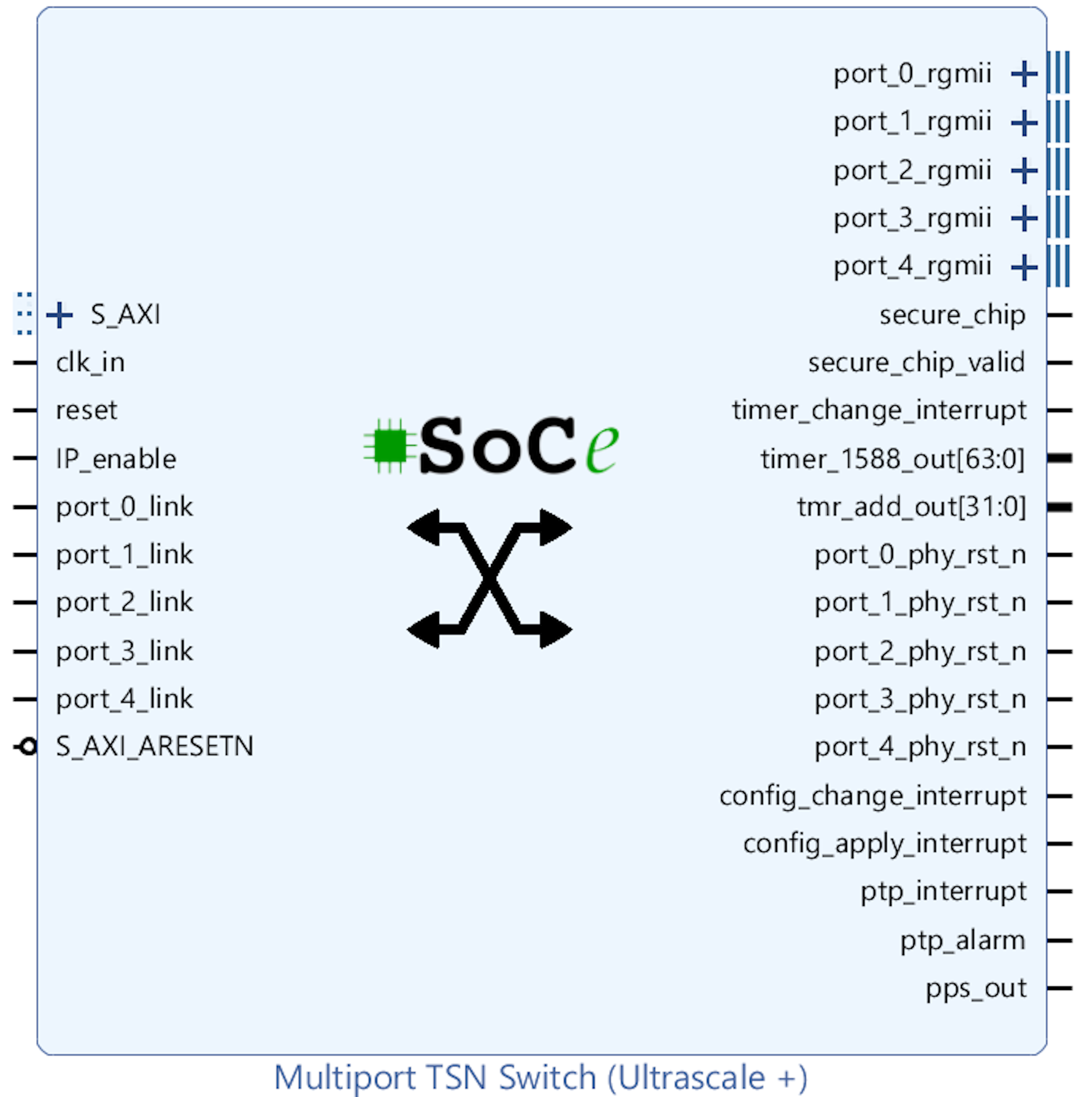

SOC-E SocTek系列IRIGtimeM IP core框图

支持的 Xilinx FPGA 系列和评估板

通过利用新的 Xilinx Vivado 工具可以轻松集成IP核到您的 FPGA 设计中,该工具允许在图形用户界面中使用 IP 核并以简单的方式配置 IP 参数。

SOC-E SocTek系列IRIGtimeM 在以下 Xilinx FPGA 系列上受支持:

- 7 系列(Zynq SoC、Spartan、Artix、Kintex、Virtex)

- 超大规模(Kintex、Virtex)

- Ultrascale+ (Zynq MPSoC、Kintex、Virtex)

- Versal ACAP

SOC-E SocTek系列产品推荐

MTSN IPcore

全面的TSN解决方案,能够实现多种TSN协议规范

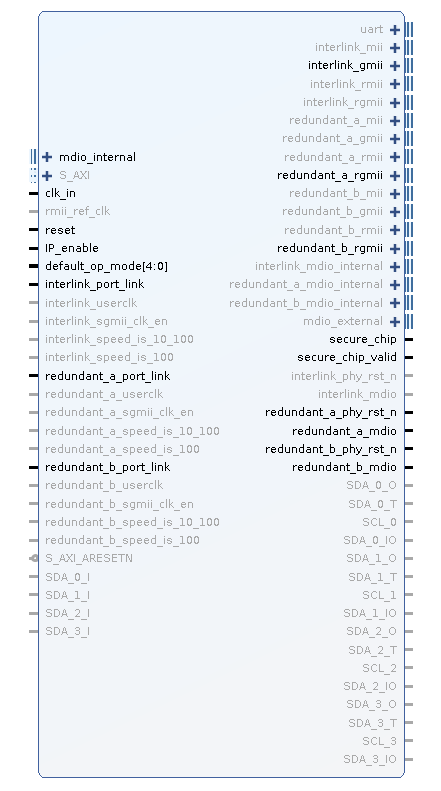

HSR/PRP/PTP IPcore

实现可靠性以太网通信的高可用性无缝冗余和并行冗余协议标准

网管/非网管IPcore

以太网交换机 IP 内核,面向可编程硬件平台

更多IPcore方案

减少设计和调试时间,加速开发进程