SOC-E SocTek系列

IRIGtimeS: IRIG-B从站IP核

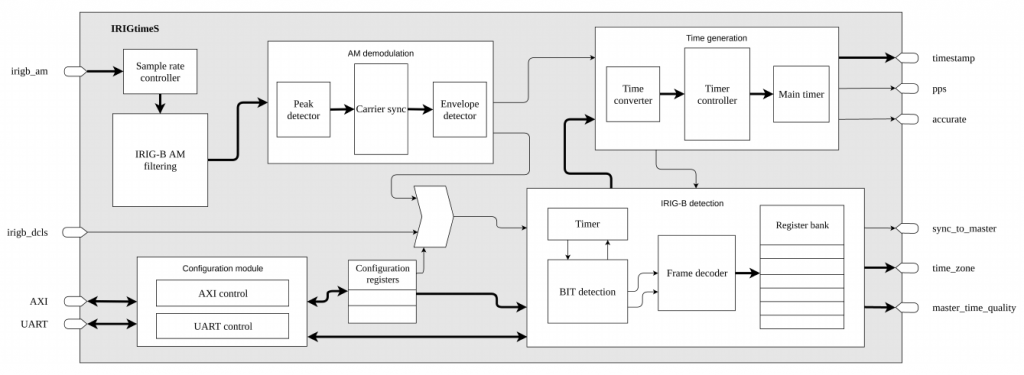

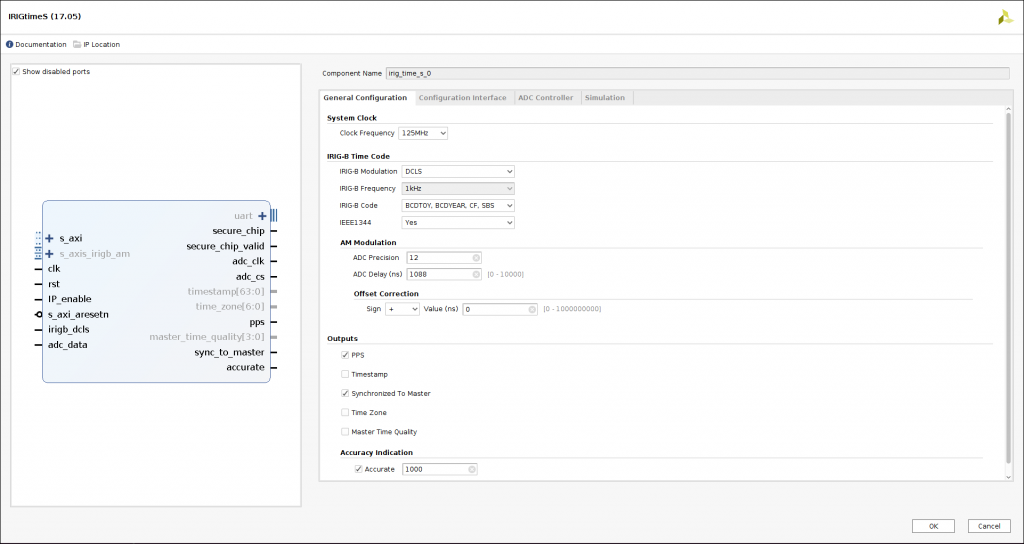

SOC-E SocTek系列IRIGtimeS 在 FPGA 设备上实现了符合 IRIG 200-04 的时间同步从站。该 IRIG-B 从 IP 旨在支持所有 IRIG-B 编码表达式以及 DCLS 和 AM 调制,以提供最大的灵活性。

SOC-E SocTek系列IRIGtimeS 从 IP 每秒接收 IRIG-B 帧,根据 IRIG-B 时间码获取时间信息(秒、分、小时、天、年、控制功能和二进制直秒)。此 IP 实现 64 位内部计时器,以提供时间戳(以秒为单位)和纳秒值。此计时器的值和频率与接收到的 IRIG-B 时间信息同步。该 IP 旨在提供自主操作,需要尽可能少的配置。