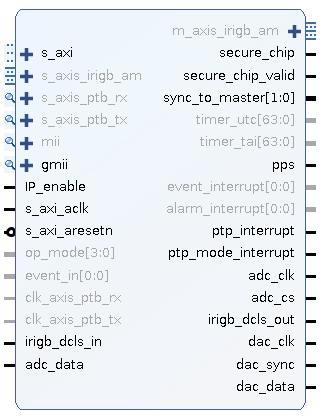

SOC-E SocTek系列MultiSync IP核的多功能性

SOC-E SocTek系列MultiSync IP核的多功能性使 MULTI同步的不同使用案例具有互补性:

- 它可以提供时间同步冗余,从而可以同时将 IP 连接到 PTP 网络和 IRIG-B 主站。用户可以在三个可用时间源(PTP、IRIG-B、自由运行计时器)之间选择使用哪个时间源

- 它可以充当 PTP 到 IRIG-B 或 IRIG-B 到 PTP 的桥接,同时 IP 与选定的主站同步

- 它可以充当 PTP 或 IRIG-B grandmaster

支持以下同步输入源

- PTP:以太网PTP 从站在输入

- IRIG-B:IRIG-B 兼容信号。IRIG-B 输入端的从站

- 自由运行定时器:数字输入

支持以下同步输出选项

- PTP:以太网。输出端的 PTP 主服务器

- IRIG-B:IRIG-B 兼容信号。IRIG-B 输出端的从站

- 自由运行定时器:数字输出

主要特点

- 多协议冗余时间同步

- 同时支持 IEEE 1588-2008 (PTPv2) 和 IRIG-B 时间同步协议

- 12 种不同的操作模式

- 3 个独立的 64 位可调定时器,与每个从机相关联。(32 位亚纳秒频率调整

- 提供每秒一个脉冲输出

- 支持事件时间戳(最多同时 4 个不同的事件)

- 支持警报检测(最多同时 4 个不同的警报)

PTP 功能

- 支持 10/100/1000 Mbps 以太网操作

- 支持的 AXI-S 接口:

- 1 Gb 以太网:8 位数据宽度

- 10 Gb 以太网:64 位数据宽度

- 选择以太网帧是否包含前导码

- 16 位 FIFO 深度。存储旧的时间戳值以避免超限

- 端到端和点对点延迟机制支持

- 在第 2 层(以太网)和第 3 层 (IPv4) 接口上支持 PTP

- 支持 VLAN 标记的 PTP 消息

- IEEE1588配置文件:默认、电源、电源实用程序 (IEC61850-9-3)、AS

IRIG-B Slave 特性

- 支持 DCLS 和 AM 调制

- AM 信号的内部滤波

- 支持所有 IRIG-B 编码表达式,包括年份信息、控制函数和直接二进制秒

- IEEE-1344 扩展支持

- 输入类型(IRIG-B 时间码)可在实施前和动态中进行配置

- 实现与 SPI、QSPI 和 MICROWIRE 协议兼容的通用 ADC 控制器

IRIG-B Master 特性

- 支持 DCLS 和 AM 调制

- 支持所有 IRIG-B 编码表达式,包括年份信息、控制函数和直接二进制秒

- IEEE1344 扩展支持

- 输出类型(IRIG-B 时间码)可在实施前和动态中进行配置

- 实现与 SPI、QSPI 和 MICROWIRE 协议兼容的通用 DAC 控制器

Free Running Timer 功能

- 完全由用户管理 (时间和频率调整)

想了解更多信息,欢迎通过info@intelnect.com联系虹科

支持的 Xilinx FPGA 系列和评估板

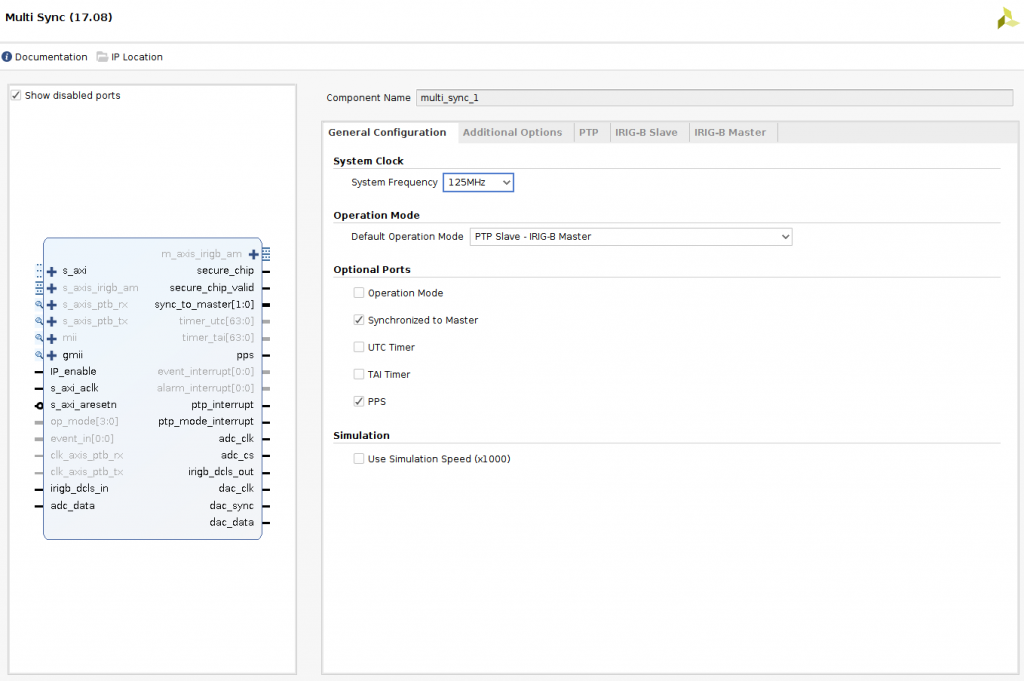

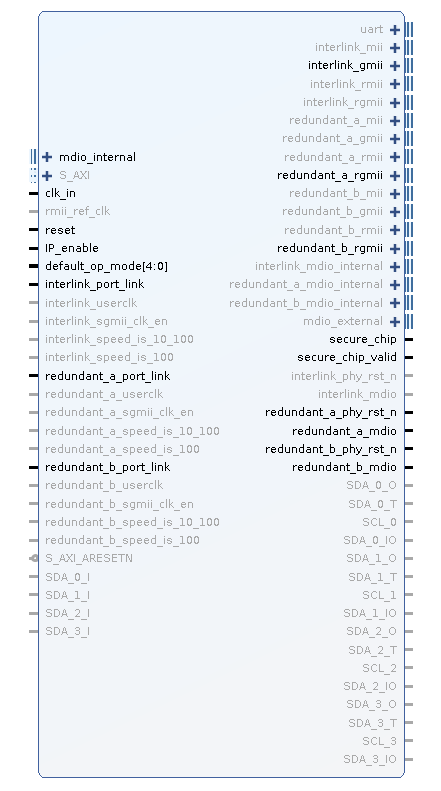

SOC-E SocTek系列MULTIsync 旨在通过利用新的 Xilinx Vivado 工具轻松集成到您的 FPGA 设计中,该工具允许在图形用户界面中使用 IP 核并以简单的方式配置 IP 参数。

以下 Xilinx FPGA 系列支持 SOC-E SocTek系列MULTI同步:

- 7 系列(Zynq、Spartan、Artix、Kintex、Virtex)

- 超大规模(Kintex、Virtex)

- Ultrascale+ (Zynq MPSoC、Kintex、Virtex)

- Versal ACAP

参考设计支持的电路板:

- SoC-e SMARTzynq 模块(推荐)

SOC-E SocTek系列产品推荐

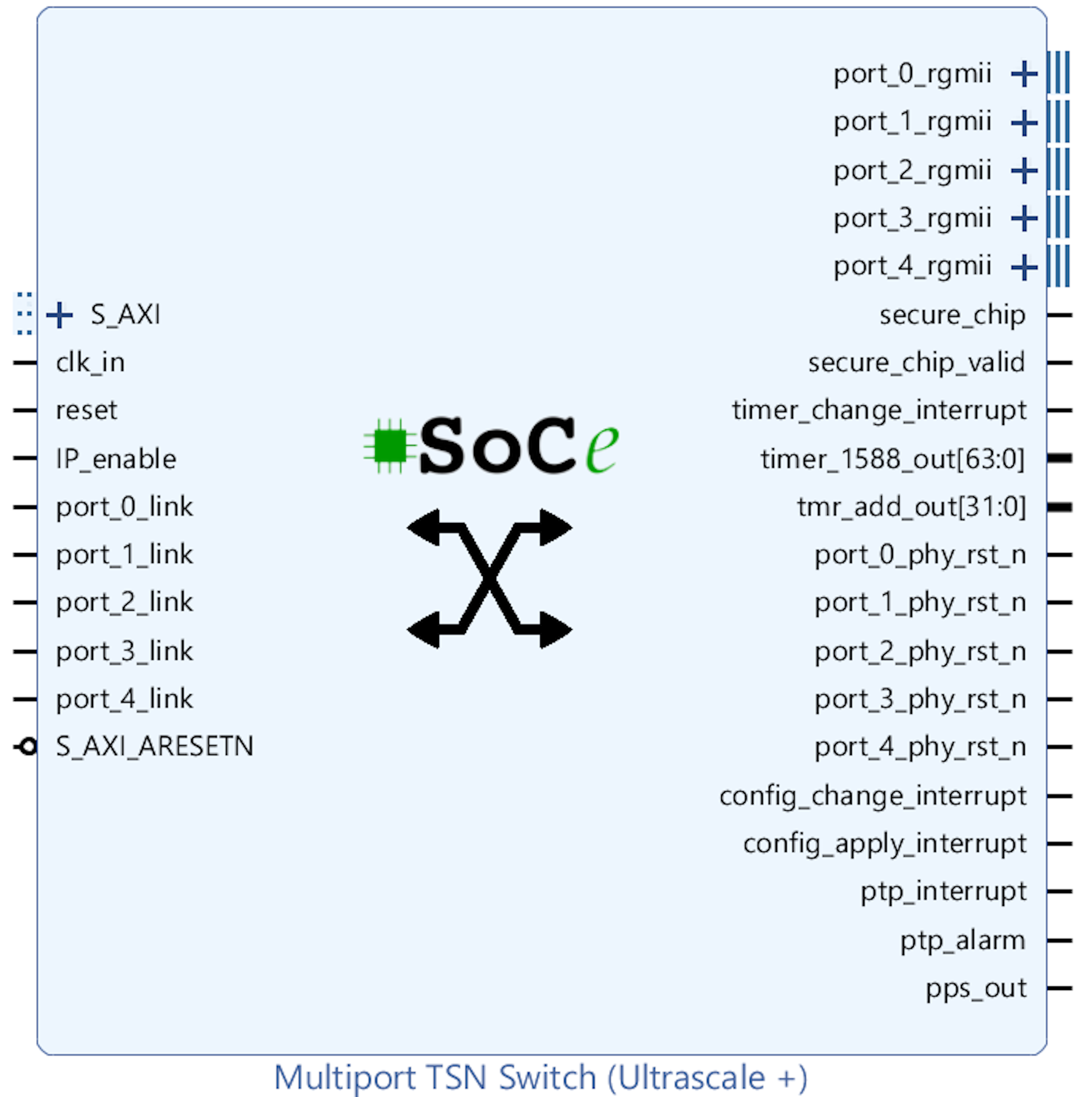

MTSN IPcore

全面的TSN解决方案,能够实现多种TSN协议规范

HSR/PRP/PTP IPcore

实现可靠性以太网通信的高可用性无缝冗余和并行冗余协议标准

网管/非网管IPcore

以太网交换机 IP 内核,面向可编程硬件平台

更多IPcore方案

减少设计和调试时间,加速开发进程